CAD-Infrastruktur für Forschung und Lehre auf dem Gebiet Analog Chip Design#

Von

Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl

Dipl.-Ing. Dr.techn. Mario Auer

Ass.-Prof. Dipl.-Ing. Dr.techn. Peter Söser

Institut für Elektronik

Der Entwurf gemischt analog/digitaler Schaltkreise ist von großer Bedeutung für mikroelektronische Systeme von heute. Die lokale Mikroelektronik-Industrie im südösterreichischen Raum ist auf diesem Gebiet sehr aktiv und hat hier einen nachhaltig hohen Bedarf an gut ausgebildeten F&E-MitarbeiterInnen. Daher unterstützen insgesamt 7 Firmen (austriamicrosystems, Dialog Semiconductors, Infineon, Micronas, NXP, Sensor Dynamics und Texas Instruments) den Aufbau von Forschung und Lehre in diesem Bereich durch Sachleistungen und Vortragende, aber auch finanziell.

© Forschungsjournal SS 07

Damit wurde es möglich, mit einer Investitionssumme von ca. € 60.000 eine leistungsfähige Infrastruktur für den Entwurf von Chips aufzubauenbzw. die bestehenden Einrichtungen den gestiegenen Anforderungen (z.B. Arbeit der Studierenden von zu Hause aus) anzupassen. Es konnten so auch neue kooperative Forschungsprojekte (FIT-IT) sowie die ersten Vorlesungen aus der neuen Analog- Chip-Design-Ausbildung (Wahlfachkatalog im E-Technik Masterstudium) unter Einsatz von modernster Hard- (SUN Client- Server-Architektur) und Software (Cadence Design Framework) begonnen bzw. durchgeführt werden.

Grundlage für den Entwurf integrierter Schaltkreise sind Technologiedaten der Halbleiterhersteller, die eine Beschreibung der Zieltechnologie sowie der Eigenschaften der verfügbaren Bauelemente beinhalten. Sie sind meist streng vertraulich, ermöglichen aber erst die sinnvolle Verwendung der CAD-Werkzeuge und damit eine zielgerichtete Forschungstätigkeit. Derzeit stehen für Forschungsaufgaben Daten von IBM, UMC und austriamicrosystems zur Verfügung, letztere werden auch in der Lehre eingesetzt. Praktische Erfahrungen der Studierenden sind im Bereich des Chip- Designs von größter Bedeutung, da erst nach der Fertigung die tatsächliche Qualität des Entwurfs evaluiert werden kann. austriamicrosystems wird diese Entwürfe daher laufend in Silizium produzieren. Die Auswertung im Labor schließt dann den Kreis des Erfahrungsgewinns.

© Forschungsjournal SS 07 / Foto: TU Graz/Inst.f.Elektronik

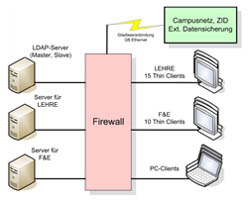

Das Institut kooperiert mit den Halbleiterherstellern der Region sehr erfolgreich und muss die Technologie-Parameter dieser Firmen sowie alle damit verbundenen Daten und Ergebnisse der Projekte entsprechend schützen. Deshalb wurde die Infrastruktur mit einer zentralisierten Rechteverwaltung sowie getrennten Rechnersystemen für Lehre und kooperative Forschung ausgestattet und somit ein Höchstmaß an Sicherheit für vertrauliche Daten implementiert. Zugleich kann den Studierenden am Institut die Möglichkeit geboten werden, die Werkzeuge und Arbeitsabläufe der Halbleiterindustrie in einer professionellen Umgebung zu erlernen. Bild 1 zeigt eine schematische Darstellung der Infrastruktur, die teilweise gemeinsam mit Experten aus der Industrie optimiert wurde. Diese Zusammenarbeit hat auch zur Folge, dass die Arbeits- und Entwurfsabläufe (Design-Flows) immer dem aktuellen Stand der Technik entsprechen, was Forschungund Lehre gleichermaßen zugute kommt.

Bild 2 zeigt einen Blick in das CAD-Labor anlässlich der Vorlesung "Layout Techniken"“, wobei der Vortragende die Vortragsinhalte bzw. den Übungsablauf live projiziert, während die Studenten an den Arbeitsplätzen die jeweiligen Aufgaben selbst praktisch nachvollziehen können. In diesem Umfeld kommen die Vorteile der gewählten Hardware-Architektur mit einem leistungsstarken, zentralen Server und den daran angebundenen lüfterlosen Clients voll zur Geltung. Die anlässlich der Gebäudesanierung im Jahr 2006 durchgeführte Erneuerung der Netzwerkinfrastruktur war für die Realisierung dieses Konzeptes sehr wertvoll.

Derzeit laufen am Institut Forschungsprojekte zu folgenden Themen:

- DA-Umsetzer für mobile Audio-Geräte (austriamicrosystems)

- RFID- (Radio Frequency Identification) Transponderschaltungen

- schnelle serielle Interfaces, z.B. für Massenspeicher (Infineon)

- Modellierung von Low Noise On Chip Stromversorgungen (Infineon)

Am Institut laufen derzeit 15 Dissertationen sowie eine Reihe von Diplom-und Projektarbeiten mit Themen aus dem Bereich Chip-Design.